# Design of a high-voltage radiation-tolerant driver with a novel comparator and drain-surrounding-source structure

Wei Huang<sup>1</sup> · Hong-Xia Liu<sup>1</sup> · Xing-Guo Gao<sup>2</sup>

Received: 22 April 2024 / Revised: 27 June 2024 / Accepted: 1 July 2024 / Published online: 7 May 2025

© The Author(s), under exclusive licence to China Science Publishing & Media Ltd. (Science Press), Shanghai Institute of Applied Physics, the Chinese Academy of Sciences, Chinese Nuclear Society 2025

#### **Abstract**

This article introduces a novel 20 V radiation-hardened high-voltage metal—oxide—semiconductor field-effect transistor (MOSFET) driver with an optimized input circuit and a drain-surrounding-source (DSS) structure. The input circuit of a conventional inverter consists of a thick-gate-oxide n-type MOSFET (NMOS). These conventional drivers can tolerate a total ionizing dose (TID) of up to 100 krad(Si). In contrast, the proposed comparator input circuit uses both a thick-gate-oxide p-type MOSFET (PMOS) and thin-gate-oxide NMOS to offer a high input voltage and higher TID tolerance. Because the thick-gate-oxide PMOS and thin-gate-oxide NMOS collectively provide better TID tolerance than the thick-gate-oxide NMOS, the circuit exhibits enhanced TID tolerance of > 300 krad(Si). Simulations and experimental date indicate that the DSS structure reduces the probability of unwanted parasitic bipolar junction transistor activation, yielding a better single-event effect tolerance of over  $81.8 \text{ MeV} \text{ cm}^2 \text{ mg}^{-1}$ . The innovative strategy proposed in this study involves circuit and layout design optimization, and does not require any specialized process flow. Hence, the proposed circuit can be manufactured using common commercial  $0.35 \,\mu\text{m}$  BCD processes.

$\textbf{Keywords} \ \ \text{Total ionizing dose (TID)} \cdot \text{Single-event burnout (SEB)} \cdot \text{High-voltage driver} \cdot \text{Comparator input unit} \cdot \text{Drain-surrounding-source ring structure}$

### 1 Introduction

High-voltage drivers are used to drive power metal-oxide-semiconductor field-effect transistors (MOS-FETs), which are widely applied in power systems, motor drive systems, and radar transceivers of satellites [1–4]. However, radiation in aerospace can reduce chip performance in high-voltage drivers, occasionally causing total system failure.

The total ionizing dose (TID) significantly affects MOSFET performance. Furthermore, the chips used in

This work was supported by the National Natural Science Foundation of China (U2241221).

- ☐ Hong-Xia Liu hxliu@mail.xidian.edu.cn

- School of Microelectronics, Xidian University, Xi'an 710000, China

- No. 24 Research Institute, China Electronics Technology Group Corporation, Chongqing 401332, China

high-voltage applications require a MOSFET with a thick gate oxide to ensure a high gate-to-source voltage ( $V_{\rm GS}$ ). However, the number of trap holes generated in response to the TID effect increases with the thickness of the gate oxide. Consequently, in conventional chips, the threshold voltage  $V_{\rm TH}$  of an n-type MOSFET (NMOS) may drop below 0 V after TID irradiation, leading to the inadvertent activation of the system despite the absence of an additional gate bias [5–8].

The single-event effect (SEE) occurs when high-energy protons and heavy ions in space collide with the sensitive nodes of a microelectronic device, generating an additional charge through ionization. This charge alters the logic state of a device, leading to functional interference or even device failure [9–11]. Conventional high-voltage drivers are vulnerable to SEE. Moreover, during SEE episodes, the parasitic bipolar junction transistor (BJT) in high-voltage MOSFETs is more susceptible to unwanted turn-ons than that in low-voltage MOSFETs [12].

Several new strategies have been developed for fabricating radiation-hardened MOSFET chips [13]. To improve

TID tolerance, Lei et al. proposed that the replacement of the typical high-voltage NMOS transistor in the output circuit of a driver with an n-p-n transistor to avoid performance degradation after TID irradiation [14]. However, the SEE or TID tolerance of the chip during the high-voltage input stage was not examined. Aubuchon et al. explored a new production method for MOSFET gate oxides that changed the temperature, environment, and steps of the oxidation process to reduce the oxide defect charge induced by TID irradiation. The resulting MOSFETs exhibited higher TID tolerance than those produced through conventional processes [15, 16]. However, the process flow cannot be integrated into conventional commercial processes, which significantly limits the application of this strategy.

Similarly, researchers have attempted to improve SEE tolerance by developing single-event-hardened devices to reduce the possibility of parasitic BJT activation. For example, Dodd et al. proposed a method that involved the addition of a buried P+ layer under the source of the MOSFET. They employed a heavily doped body contact and incorporated a heavily doped P+-buried layer underneath the source [17]. However, this P+ buried layer required a unique fabrication method that did not align with traditional bipolar complementary metal-oxide-semiconductor (CMOS)-doublediffused metal-oxide-semiconductor (DMOS) (BCD) processes. Previously, we developed a layout optimization strategy that increased the length of the n-type drift region in the n-type channel lateral double-diffused metal-oxide-semiconductor field-effect transistor (NLDMOS) to improve the SEE tolerance of the device. This method reduced the amplification of the parasitic BJT and electric field intensity of the drift region at the same voltage by increasing the length of the drift region, which increased the chip area [18]. However, the aforementioned studies primarily focused on the development of radiation-tolerant output circuits, and few studies on radiation-tolerant methods that target input circuits have been performed.

In this paper, we present a comparator input unit and level shift unit that increase the TID tolerance of a MOSFET driver and a novel DSS ring structure that increases its SEE tolerance. Notably, p-type MOSFETs (PMOS) exhibit better TID tolerance than NMOS. Hence, we developed a comparator using a high-voltage PMOS with a thick gate oxide and a low-voltage NMOS with a thin gate oxide to replace the high-voltage thickgate-oxide NMOS present in conventional input circuits. Our experiments indicated that the functional parameters of the chips containing this novel comparator remained normal even at a TID of 300 krad(Si), whereas those of the unreinforced chips were altered at a lower TID of 100 krad(Si). We also conducted simulations to assess the SEE tolerance of two types of NLDMOS devices featuring different source and drain locations, which were fabricated based on the ring-gate structure required for TID tolerance. The results indicated that the NLDMOS with a DSS structure exhibited better SEE tolerance than that with an SSD structure. Subsequently, the experimental results confirmed that the chip with the novel DSS structure withstood an SEE greater than 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>. Finally, we identified the sensitive regions of the chip under single-particle irradiation, providing an intuitive and effective strategy for positioning other sensitive regions under these conditions.

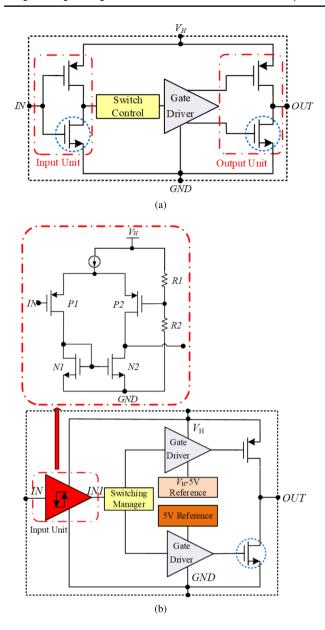

# 2 Characteristics of conventional (unreinforced) high-voltage drivers

The schematic of a typical unreinforced high-voltage driver circuit consisting of an input unit, a switching manager, a gate driver, and an output unit is presented in Fig. 1a. To ensure that both the input and output voltages reached 20 V, NMOS and PMOS with 1000 Å thick gate oxides were used in the input and output units of a typical high-voltage driver circuit because the gate oxide thickness is associated with  $V_{\rm GS}$ .

TID irradiation increases leakage currents [19, 20] primarily because of the parasitic currents between the drain and source of the NMOS, which are induced by the exit of the field oxide layer under TID irradiation. Moreover, a thick oxide layer results in a more severe TID effect, and the  $V_{\mathrm{TH}}$  shift induced by the TID is proportional to the square of the oxide thickness. Therefore, the fixed charge density produced by the TID effect can increase the gate-to-source leakage current in the thick-gate-oxide NMOS devices. This results in a negative  $V_{\text{TH}}$  shift, rendering the NMOS vulnerable to unwanted turn-on.  $V_{TH}$  can shift below 0 V after TID irradiation, which impairs driver function, particularly in high-voltage thick-gateoxide devices. Furthermore, CMOS circuits are susceptible to latch-up owing to attacks by high-energy particles, which can cause unwanted parasitic BJT device turn-on in a thyristorlike mode [21, 22]. The energy transferred from the incident particles produces electron-hole pairs (EHPs), which alter the electric field distribution of the epitaxial layer and activate the parasitic BJTs, eventually triggering single-event burnout (SEB). The drain current of the NMOS continues to increase until burnout occurs. Hence, the TID and SEB tolerances of typical high-voltage drivers are extremely low. Therefore, the structure shown in Fig. 1a cannot resist TID and SEE irradiation and the chip exhibits impaired function or damage after irradiation in space.

# 3 Design of a radiation-tolerant high-voltage driver

### 3.1 TID-tolerant design with a comparator input unit

The oxide trap charge produced by the TID in the gate oxide layer of NMOS devices causes a negative shift in

**Fig. 1** (Color online) Schematics of the typical and radiation-resistant drivers. **a** Schematic of the traditional driver circuit; **b** structure of the proposed radiation-resistant driver

$V_{\rm TH}$ . Hence, the high-voltage thick-gate-oxide NMOS experiences a more severe TID effect. The isolation oxide is instrumental in the TID response of the device, because its thickness is much greater than that of the gate oxide. Here, the number of charges increases with the ionizing dose, which results in substrate depletion or even inversion. Thus, the device becomes depleted and cannot be shut off normally. Owing to the extremely low TID tolerance of high-voltage NMOS, the design of the input circuit must be optimized. As described earlier, the reduced  $V_{\rm TH}$  of PMOS prevents the device from continuously remaining on. Hence, we designed a comparator comprising

high-voltage PMOS and low-voltage NMOS devices (Fig. 1b). As this comparator design lacks a high-voltage NMOS, which is most susceptible to TID irradiation, it exhibits enhanced TID tolerance.

A high-voltage PMOS named P1 with a 1000 Å thick gate oxide was used as the input device in the input unit of the comparator structure (Fig. 1b). Because the NMOS is located on the p-type substrate, the accumulated charge in the isolated oxide layer increases with the total dose. This accumulated charge can invert the substrate under the isolated oxide layer from p- to n-type, forming n-type channels and parasitic NMOS transistors. The parasitic NMOS was parallel to the main transistor and significantly increased the turn-off leakage current. However, because the PMOS was located in the N-well, the trap charges generated in the isolated oxide layer after TID irradiation did not cause n-type interface inversion. Hence, the leakage current generated by TID irradiation in the PMOS was minimal [23–25]. Consequently, PMOS performed better than NMOS against TID irradiation.

The resistances R1 and R2 provide the reference voltage for the comparator.  $V_{GS}$  of the thick-gate-oxide PMOS device was above 24 V, satisfying the maximum input requirement of 20 V. The sources of the two thick-gate-oxide PMOS devices (P1 and P2) were connected to a high voltage  $V_{\rm H}$ , which was equal to the supply voltage of 20 V in this circuit. The gate of P1 was used as the input of the comparator, while the drain of P1 was connected to the drain of the NMOS with a 200 Å thin gate oxide (N1). The drain of P2 was connected to the drain of the NMOS with a 200 Å thin gate oxide (N2), and the drain of N1 was connected to the gate. The sources of N1 and N2 were connected to the GND. When the input voltage was lower than 0.8 V,  $V_{\rm GS(P1)}$  was greater than  $V_{\rm GS(P2)}$ , and the current generated on  $V_{\rm H}$  primarily flowed through P1 and N1. Hence, P1, N1, and N2 were on; the output voltage IN1 was close to GND; and the output was low. The simulation analysis indicated that the output voltage IN1 was approximately 1 mV under these conditions. In contrast, when the input voltage was higher than 2.4 V,  $V_{GS(P1)}$  was lower than  $V_{GS(P2)}$ , and the current generated from  $V_{\rm H}$  primarily flowed through P2 and N2. P2 was open; hence, output voltage IN1 was close to  $V_{\rm H}$ . Thus, the output was high, and the simulation analysis indicated that the output voltage IN1 under these conditions was approximately 4 V.

Meanwhile, the  $V_{\rm TH}$  shift in the PMOS after TID irradiation did not affect the function of the comparator. In the comparator, the irradiation performance degradations of the high-voltage PMOS (P1 and P2) and low-voltage NMOS (N1 and N2) devices were synchronized. This eliminated the influence of the  $V_{\rm TH}$  shift of the single NMOS, preventing alterations in the current distribution of the input structure and output voltage IN1 of the comparator after irradiation.

**115** Page 4 of 10 W. Huang et al.

Therefore, this structure improves the TID tolerance of high-voltage input structures.

For the output circuit, we employed a previously reported level shift unit method to increase the TID tolerance [19] (Fig. 1b). The level shift unit in this radiation-resistant circuit generated references of 5 V and  $V_{\rm H}$ -5 V. The 5 V and  $V_{\rm H}$ -5 V references were applied to the gates of the NMOS and PMOS, respectively. Hence, the gate voltage of the MOSFET in this circuit was reduced to 5 V, enabling the adoption of a thin-gate-oxide device. Meanwhile, an LDMOS with a VGS of +5 V and drain-source voltage ( $V_{\rm DS}$ ) of 20 V was used as the output device to achieve an output voltage of 20 V along with good TID tolerance. Overall, this design provided higher radiation tolerance to the driver by eliminating the use of the TID-sensitive thick-gate-oxide NMOS through the design of the harden schematic.

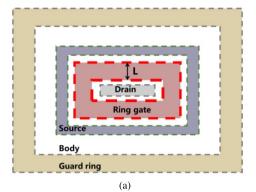

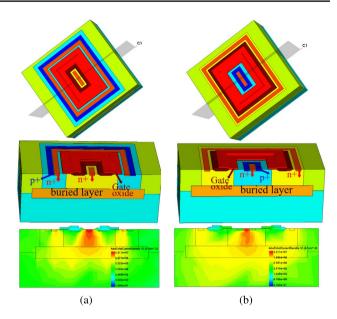

### 3.2 SEE-tolerant design using a novel NLDMOS structure

To reduce the single-particle-induced current in MOSFET, both SSD and DSS configurations were designed based on an enclosed-layout transistor (ELT) structure, as shown in Fig. 2a and b, respectively. As shown in Fig. 2, the body region surrounding the source in the DSS structure is smaller than that in the SSD structure. Hence, the P-region area of the parasitic NPN transistor is smaller. Consequently, the amount of charge triggered following the single-particle irradiation is less than that triggered in the device with the SSD structure, leading to a lower probability of unwanted parasitic BJT turn-on. Therefore, the DSS structure provides stronger SEE tolerance than the SSD structure.

### 3.3 Design of the overall layout of the high-voltage radiation-tolerant driver

The method proposed to increase the radiation tolerance in this study is based on a commercial process. Importantly, it does not involve any modifications to the process flow because the layout is adjusted without altering basic processes or manufacturing steps employed for fabricating common devices. By optimizing the chip layout, as mentioned in the previous section, the leakage current generated by the TID effect and the current concentration effect generated by the SEE can be mitigated. This is because MOSFETs have an ELT gate layout that eliminates the leakage channel created between the source and drain of the edge of the field oxide caused by the TID effect. Additionally, adjusting the positions of the source and drain in MOSFETs with an ELT gate layout can reduce the current induced via single-particle irradiation.

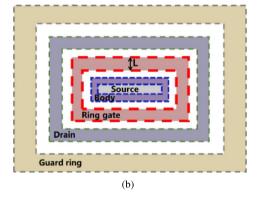

The overall layout of the high-voltage driver was symmetrical (Fig. 3). Four independent driver channels were

**Fig. 2** (Color online) Structural layout of the NMOS. **a** Source-surrounding-drain (SSD) structure; **b** drain-surrounding-source (DSS) structure

integrated into one chip to enable multichannel driving. All four channels shared an input stage and a power supply unit. In the layout, the input device was next to the input port; the reference, buffer, and level shift unit were at the center of the overall layout to provide a bias voltage or input to other devices. The output device was next to the output port, and the output NMOS and PMOS devices were symmetrically distributed such that the PMOS of the two channels shared an N-well, which reduced the layout area. A three-layer wiring design was adopted to reduce the layout area and increase the degree of integration. Additionally, electrostatic discharge (ESD) protection devices were installed near all the input/output (I/O) and power ports to improve the ESD tolerance of the driver. The NMOS in the layout adopted two structures based on the SSD and DSS configurations.

### 4 Irradiation experiments

Four types of chips were fabricated using a commercial 0.35-µm BCD process, as listed in Table 1. A common commercial process provided the high-voltage devices required for this design, and the fabrication of these chips was cost-effective and suitable for this application. The Type 1 and

Fig. 3 (Color online) High-voltage radiation-resistant driver layout with a four-channel symmetrical structure

Table 1 Description of the four types of chips fabricated

| Device | Input structure      | NMOS layout |

|--------|----------------------|-------------|

| Type 1 | Typical structure    | SSD         |

| Type 2 | Typical structure    | DSS         |

| Type 3 | Comparator structure | SSD         |

| Type 4 | Comparator structure | DSS         |

Type 2 chips used a typical input structure with different NMOS layouts in the SSD and DSS configurations, while the Type 3 and Type 4 chips used a comparator input structure with different NMOS layouts in the SSD and DSS configurations. The area of all the chips was 3.3 mm  $\times$  2.5 mm because this design was compatible with the package structure of the chips and test system for the subsequent experiments. Before the irradiation experiment, the basic functional parameters of the four chips were tested. The results indicated that the basic functional parameters of all the four chips satisfied the design index requirements. All the four chips exhibited normal output waveforms corresponding to a high-frequency input signal of 40 MHz. In addition, no significant differences in the output waveforms of the chips were observed, indicating that the input structure and NMOS layout did not significantly affect the high-frequency and high-voltage output performances of the chips. Nevertheless, slight differences in the tested and emulational output waveforms were observed owing to the influence of the parasitic loads generated by the test system. Subsequently, TID and SEE irradiation experiments were performed to evaluate the performances of the four chips, as described below.

### 4.1 TID experiments

The TID experiments were conducted at the Xinjiang Technical Institute of Physics and Chemistry, Chinese

Academy of Sciences, China. Co-60 was used as the radiation source, and three different irradiation doses, i.e., 100 krad(Si), 200 krad(Si), and 300 krad(Si), with a dose rate of 50 rad(Si) s<sup>-1</sup>, were selected. A 20 V program-controlled power supply was used to supply power to the test samples, and a signal source was used to provide a 40 MHz high-frequency input signal. A customized automatic test system was employed to test the key electrical parameters of the chips (drain current  $(I_d)$ , input low voltage  $(V_{IL})$ , and supply current  $(I_{SL})$ ) before and after irradiation to observe the effect of TID [26–28]. The devices were tested 20 min after irradiation to reduce the annealing effect.

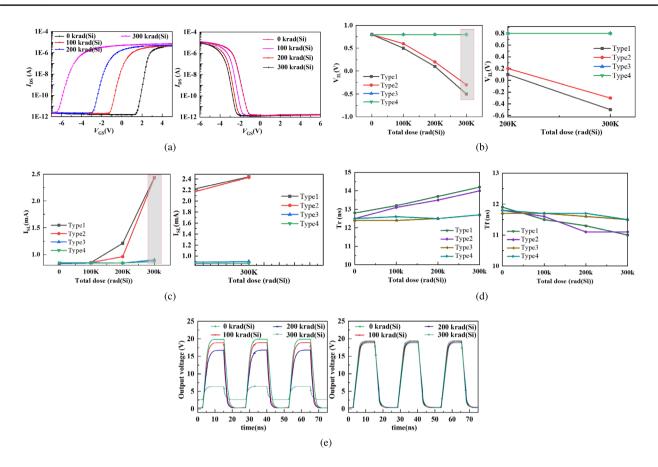

The basic functional parameters of the high-voltage driver, that is,  $I_d$ ,  $V_{IL}$ ,  $I_{SL}$ , rise time  $(T_r)$ , and fall time  $(T_f)$ , were evaluated before and after TID irradiation (Fig. 4). Here  $V_{\rm IL}$  denotes the tested low voltage at which the input unit functions normally;  $I_{SL}$  represents the supply current at the input voltage  $V_{IN} = 0$  V;  $T_r$  represents the rise time of the output waveform when the input is a 100 kHz square wave; and  $T_{\rm f}$  represents the fall time of the output waveform with the same input. The test data showed that the  $V_{\rm II}$  values of the two hardened devices (types 3 and 4) were above 0.8 V after 100 krad(Si), 200 krad(Si), and 300 krad(Si) irradiation.

However, the  $V_{\rm IL}$  of the two unhardened devices (types 1 and 2) shifted to 0.5 V and 0.6 V after 100 krad(Si) irradiation and to 0.1 V and 0.2 V after 200 krad(Si) irradiation, respectively. Thus, the driver provided a low output only when the input voltage was below 0.5 V and 0.6 V after 100 krad(Si) irradiation and below 0.1 V and 0.2 V after 200 krad(Si) irradiation. Additionally, the T<sub>r</sub> of the two unhardened devices (types 1 and 2) shifted from 12.8 ns and 12.5 ns to 13.2 ns and 13.1 ns after 100 krad(Si) irradiation and to 13.3 ns and 13.5 ns after 200 krad(Si) irradiation, respectively. This was attributed to the increase in the absolute value of  $V_{\rm TH}$  of the PMOS after TID irradiation, indicating a decrease in its conduction capacity and a subsequent increase in the output rise time. Meanwhile, the  $T_{\rm f}$  of the two unhardened devices (types 1 and 2) changed from 11.9 ns and 11.8 ns to 11.5 ns and 11.6 ns after 100 krad(Si) irradiation and to 11.3 ns and 11.1 ns after 200 krad(Si) irradiation, respectively. This is because the absolute value of  $V_{\rm TH}$  of the NMOS decreases after TID irradiation, increasing its conduction capacity and decreasing its output fall time. The trends of  $T_r$  and  $T_f$ are observed in the output waveforms shown in Fig. 4(e).

The static noise margin (SNM) reflects the ability of the chip to withstand static noise and can be classified into low SNM (LSNM) and high SNM (HSNM). LSNM is equivalent to the voltage difference between VIL and GND, whereas HSNM is equivalent to the voltage difference between VIH and the power supply voltage. Here, the LSNMs of the Type 1 device were 0.5 V, 0.1 V, and –

**115** Page 6 of 10 W. Huang et al.

**Fig. 4** (Color online)  $I_{\rm d}$ - $V_{\rm g}$  curves of the thick-gate-oxide NMOS and PMOS, parameter test results, and output waveforms of the driver before and after the TID experiment. a  $I_{\rm d}$ - $V_{\rm g}$  curves of thick-gate-

oxide NMOS and PMOS before and after the TID experiment;  $\mathbf{b}$   $V_{\rm IL}$  before and after the TID experiment;  $\mathbf{c}$   $I_{\rm SL}$  before and after TID experiment;  $\mathbf{c}$   $I_{\rm T}$  and  $I_{\rm T}$  and  $I_{\rm T}$  before and after the TID experiment;  $I_{\rm T}$  output waveforms of types 1 and 3 before and after the TID experiment

0.5 V after 100 krad(Si), 200 krad(Si), and 300 krad(Si) irradiation, respectively.

Furthermore, the  $V_{\rm IL}$  values of both unhardened devices (types 1 and 2) dropped below 0 V at a TID of 300 krad(Si) because  $V_{TH}$  of the thick-gate-oxide NMOS shifted as the total dose increased, decreasing to below 0.8 V and 0 V after 100 krad(Si) and 300 krad(Si) irradiation, respectively. Thus, the thick-gate-oxide NMOS was turned on at  $V_{\rm IL}$ =0.8 V and  $V_{IL}$ =0 V after 100 krad(Si) and 300 krad(Si) irradiation, respectively, causing the driver to constitutively stay on and behave abnormally. In addition,  $I_{\rm SL}$  increased from 0.85 mA before TID irradiation to 2.44 mA (Type 1) and 2.43 mA (Type 2) after 300 krad(Si). This is because certain devices inside the driver could not be turned off under these test conditions, thereby increasing the leakage current. In contrast, all tested  $V_{\rm IL}$ ,  $I_{\rm SL}$ ,  $T_{\rm r}$ , and  $T_{\rm f}$  values for the hardened Type 3 and Type 4 devices remained stable before and after TID irradiation.

The results presented in Fig. 4 suggest that the functional parameters of the two hardened devices with the novel comparator structure remained normal after 300 krad(Si) TID

irradiation, which aligns with our proposed design. This suggests that the input high-voltage comparator composed of the thick-gate-oxide PMOS and thin-gate-oxide NMOS exhibits improved TID tolerance, and the influence of the  $V_{\rm TH}$  shift and leakage current in the input high-voltage comparator following TID irradiation is significantly weaker than that in a typical high-voltage driver.

### 4.2 SEE experiments

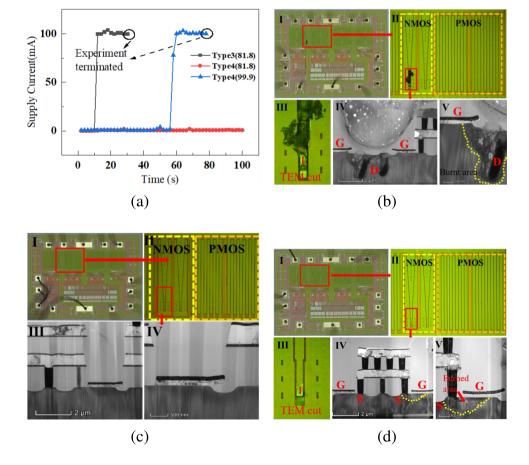

Subsequently, we used TID-hardened Type 3 and Type 4 devices for the SEE experiments. These experiments were conducted at the Institute of Modern Physics, Chinese Academy of Sciences, using the heavy-ion research facility at Lanzhou (HIRFL), with different accelerating particles with a linear energy transfer (LET) ranging from 8 to 100 MeV cm<sup>2</sup> mg<sup>-1</sup> [29–31].

Ti and Bi ions (LET =  $81.8 \text{ MeV cm}^2 \text{ mg}^{-1}$  and  $99.9 \text{ MeV cm}^2 \text{ mg}^{-1}$  and ion emission distances in Si = $27.3 \mu \text{m}$  and  $15.2 \mu \text{m}$ , respectively) were selected. The ions were almost vertically incident on the chips and the ion fluence

was  $10 \times 10^7$  cm<sup>-2</sup>. Heavy ions collide with semiconductor materials, creating an ionization path with high charge density and activating the parasitic BJT in the MOSFETs. The power supply voltage was 20 V. A square wave was adopted as the input signal to control the MOSFETs, and the driver input was programmed to be 0 V or 20 V. While increasing the ion dose from 0, the changes in the power supply current and output voltage were monitored at recording intervals of 1 s using an ammeter and oscilloscope, as single-particle irradiation typically induces a current pulse first. To ensure safety, the maximum probing power supply current was set to 100 mA. Three samples were selected for each experimental condition to avoid the inherent influence of the samples on the test results.

The test results revealed the variations in the power supply current with the ion implantation time in the two devices. The power supply current of the Type 3 device increased from 0.3 mA to a limit of 100 mA in approximately 12 s at LET=81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>. Because the Type 3 device failed at 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>, it was not used for subsequent experiments at higher LET values. In comparison, the power supply current and output waveform of the Type 4 device remained normal at 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>, while its power supply current increased from approximately 0.7 mA to the limit of 100 mA in approximately 60 s at LET= 99.9 MeV cm<sup>2</sup> mg<sup>-1</sup>. The findings in Fig. 5a demonstrate that the SEE tolerance of the Type 3 device is below 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>. In contrast, the Type 4 device endured 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> but failed at a higher LET of 99.9 MeV cm<sup>2</sup> mg<sup>-1</sup>.

A high-magnification optical microscope (OM) and a transmission electron microscope (TEM) were used to further observe the SEE-sensitive regions of the chip and the burnout area. Some fault points were detected in the chips after the 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> and 99.9 MeV cm<sup>2</sup> mg<sup>-1</sup> SEE experiments for the types 3 and 4, respectively.

First, we examined the test chips using high-magnification OM. A noticeable burn mark was observed on the surface of the Type 3 chip after the 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> experiment (Fig. 5b). However, this chip had a multilevel design, and an upper layer of aluminum was added to its surface to ensure current flow. The internal structure of the NMOS was obscured by this top layer and could not be examined in detail by surface microscopy alone. Therefore, we performed TEM section sampling on the burned part of the aluminum wire based on the layout structure, using sections taken perpendicular to the drain. The TEM samples were prepared using the focused-ion-beam (FIB) cutting method, and the thin slices, which were only 1

Fig. 5 (Color online) Power supply current and the OM and TEM morphologies of Type 3 after 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>, Type 4 after 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> and Type 4 after 99.9 MeV cm<sup>2</sup> mg<sup>-1</sup> experiments. (a) Power supply current of types 3 and 4 over time during the SEE experiment; (b) OM and TEM morphologies of Type 3 after 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> experiment. The burnout area is the drain of the NMOS; (c) OM and TEM morphologies of Type 4 after 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> experiment. The chip is normal; (d) OM and TEM morphologies of Type 4 after 99.9 MeV cm<sup>2</sup> mg<sup>-1</sup> experiment. The burnout area is the source of the NMOS

um thick, were observed via TEM. Accordingly, the complete morphologies of the source, drain, and gate of the NMOS were observed. The TEM findings revealed that the burned area in the Type 3 chip after exposure to 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> corresponded to the drain metal wire and drain area. Hence, the drain of the NMOS with the SSD structure experienced the maximum current during SEE. In contrast, the surface of the Type 4 chip remained undamaged at the same LET of 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup> (Fig. 5c). However, an evident burn was detected on the surface of the Type 4 chip after exposure to 99.9 MeV cm<sup>2</sup> mg<sup>-1</sup>. TEM analysis revealed that this burn was near the source (Fig. 5d). The five images shown in Fig. 5b, c, and d are enlarged step-by-step in the order of I, II, III, IV, and V (marked on the upper left corner of the pictures), and the next picture is a partially enlarged picture of the figure in the red box of the previous picture. This demonstrates that upon exposure to accelerating particles, the NMOS with the DSS structure generates the maximum current in the source.

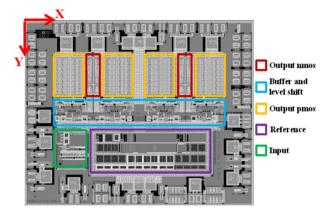

The test results for the two devices were different. To analyze the causes and mechanisms underlying these differences, three-dimensional (3D) models of the two devices were established using Sentaurus TCAD to simulate the performance of the MOSFETs under SEE exposure [32–36] (Fig. 6). The device structure of the simulation model was determined by referring to the process structure of the driver and device layout shown in Fig. 2. In the vertical direction, the device consisted of a 10 µm epitaxial layer and a 2 µm buried layer connected to a 6-µm-deep PWELL. An asymmetric gate structure with a 0.2-µm-thick field oxide was used near the source under the gate oxide layer, while a thicker 0.55 µm oxide layer was used near the drain. In the horizontal direction, the gate width  $L_G$  was 4  $\mu$ m, and both the source ( $L_{\rm S}$ ) and drain ( $L_{\rm D}$ ) widths were 2  $\mu$ m. The N+ drift region length  $L_{N+}$  was 2.4 µm. During the simulation, the drain voltage was biased at 20 V, while the gate and source voltages of the device were set to 0 V. These parameters were selected according to the commercial 0.35 µm BCD process used to fabricate the driver chips. The doping parameters of the devices were determined by the foundry, and the model parameters were calibrated according to the electrical parameters tested.

To analyze the SEE tolerance differences between the two structures, their current distributions under SEE effects were simulated using a heavy-ion irradiation model with a specific radius of 1  $\mu$ m. The direction of the heavy-ion bombardment was perpendicular to the device. The concentration distribution of EHPs was generated using a Gaussian model. The heavy-ion incidence time and LET value were 1 ns and 0.8 pC/ $\mu$ m, respectively. Under these conditions, the maximum drain current ( $I_{\rm DMAX}$ ) and current distributions of

**Fig. 6** (Color online) Simulation results of the current distributions of the SSD and DSS ELT structures. **a** Simulation results of the current distributions of the SSD under single-particle injection; **b** simulation results of the current distributions of the DSS under single-particle injection

the two device types were simulated under single-particle irradiation.

The first part of Fig. 6a or b shows the 3D models of the DSS or SSD MOSFETs, while the second and third parts depict the cross section of the first figure and internal current distribution of the two devices under SEE effects, respectively. The simulation results show that under single-particle irradiation, the  $I_{\rm DMAX}$  generated by the SSD and DSS structures were 1.16 mA and 0.73 mA, respectively.

In the SSD structure (Fig. 6a), the wider body area allowed more ion charges to be deposited during single-particle irradiation. Thus, more EHPs were generated under the same applied voltage, creating a base current and possibly turning on the parasitic BJT. This current generated a large current between the drain and source, eventually resulting in device burnout. In comparison, fewer EHPs were generated in the body region after single-particle irradiation in the DSS configuration (Fig. 6b). Thus, the current at the base of the parasitic BJT was smaller, which reduced the possibility of an unwanted parasitic BJT turning on. Therefore, the DSS structure is more resistant to single-particle irradiation than the SSD structure. However, in both SSD and DSS devices, the current was concentrated in the middle of the device (Fig. 6), which corresponded to the source and drain regions in the DSS and SSD structures, respectively. The burned areas observed after the SEE experiments (Fig. 5) were consistent with the simulation results (Fig. 6).

#### 5 Conclusion

This article introduces a radiation-tolerant 20 V high-voltage driver prepared using the commercial 0.35 µm BCD process. In this driver, a comparator is used in the input unit, with the thick-gate-oxide NMOS of conventional highvoltage drivers replaced by a thick-gate-oxide PMOS and thin-gate-oxide NMOS. Accordingly, the hardened drivers exhibited an enhanced TID tolerance of 300 krad(Si). Additionally, a DSS structure was incorporated into all the NMOS devices to increase the overall SEE tolerance. The simulation and experimental results indicated that the DSS structure prevented unwanted parasitic BJT turnon, enabling the designed chips to endure an LET of 81.8 MeV cm<sup>2</sup> mg<sup>-1</sup>. Moreover, the identification of the sensitive regions of devices with DSS and SSD structures based on morphological analysis after the SEE experiments indicates the feasibility of this strategy for effectively testing other radiation-tolerant designs. Because both the TID- and SEEhardening methods proposed in this work utilize common commercial processes and do not require any changes in the process control conditions or process flows, they can be widely and economically applied to incorporate these novel integrated circuits in aerospace systems. Moreover, the reinforcement design and verification protocols proposed in this study can serve as a reference for similar optimization strategies and be combined with other radiation-hardening design methods, such as increasing the length of the N+ drift zone, to further enhance the radiation tolerance of the chips.

**Author contributions** All authors contributed to the study conception and design. Material preparation, data collection, and analysis were performed by Wei Huang, Hong-Xia Liu, and Xing-Guo Gao. The first draft of the manuscript was written by Wei Huang, and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Data availability The data that support the findings of this study are openly available in Science Data Bank at https://cstr.cn/31253.11.scien cedb.j00186.00554 and https://doi.org/10.57760/sciencedb.j00186. 00554.

### **Declarations**

Conflict of interest The authors declare that they have no conflict of interest.

### References

- 1. W. Rosenzweig, Space radiation effects in silicon devices. IEEE T. Nucl. Sci. 12, 18-29 (1965). https://doi.org/10.1109/TNS.1965. 4323897

- 2. D.M. Fleetwood, Evolution of total ionizing dose effects in MOS devices with Moore's law scaling. IEEE T. Nucl. Sci. 65, 1465-1481 (2018). https://doi.org/10.1109/TNS.2017.2786140

- 3. X.Y. Zhao, F. Liu, Z. Deng et al., GERO: a general SCA-based readout ASIC for micro-pattern gas detectors with configurable storage depth and on-chip digitizer. Nucl. Sci. Tech. 30, 131 (2019). https://doi.org/10.1007/s41365-019-0659-2

- C. Chang, L.O. Tian, L.Y. Xiao et al., Heavy-ion and pulsed-laser single event effects in 130-nm CMOS-based thin/thick gate oxide anti-fuse PROMs. Nucl. Sci. Tech. 30, 80 (2019). https://doi.org/ 10.1007/s41365-019-0602-6

- 5. J. Liu, J.L. Duan, M.D. Hou et al., SEU ground and flight data in static random access memories. Nucl. Instrum. Methods Phys. Res. Sect. B. 245, 342–345 (2006). https://doi.org/10.1016/j.nimb. 2005.11.125

- S. Wang, X.J. Li, X.W. Cai et al., TID effect of MOSFETs in SOI BCD process and its hardening technique. IEEE T. Nucl. Sci. 60, 1995-2001 (2023). https://doi.org/10.1109/TNS.2023.3281597

- 7. J.J. Chen, Y.Q. Chi, B. Liang et al., ASET and TID characterization of a radiation hardened bandgap voltage reference in a 28-nm bulk CMOS technology. IEEE T. Nucl. Sci. 69, 1141-1147 (2022). https://doi.org/10.1109/TNS.2022.3152496

- Z.Y. Hu, Z.L. Liu, H. Shao et al., Comprehensive study on the total dose effects in a 180-nm CMOS technology. IEEE T. Nucl. Sci. 58, 1347–1354 (2011). https://doi.org/10.1109/TNS.2011. 2132145

- X. Xie, H.L. Zhu, M.Y. Zhang et al., An analytical study of the effect of total ionizing dose on body current in 130-nm PDSOI I/O nMOSFETs. IEEE T. Nucl. Sci. 66, 625-634 (2019). https:// doi.org/10.1109/TNS.2019.2897278

- 10. Q.Q. Wang, H.X. Liu, S.L. Wang et al., Total ionizing dose effect of gamma rays on H-gate PDSOI MOS devices at different dose rates. Nucl. Sci. Tech. 28, 151 (2017). https://doi.org/10.1007/ s41365-017-0295-7

- 11. B.J. Liu, L. Cai, Monte Carlo reliability model for single-event transient on combinational circuits. IEEE T. Nucl. Sci. 64, 2933-2937 (2017). https://doi.org/10.1109/TNS.2017.2772267

- Y.F. Zhao, L. Wang, S.G. Yue et al., SEU and SET of 65 bulk CMOS flip-flops and their implications for RHBD. IEEE T. Nucl. Sci. 62, 2666–2672 (2015). https://doi.org/10.1109/TNS.2015. 2490552

- 13. Z. Li, W. Huang, L.J. Zhao et al., Study of the correlation between the cutting edge current breakdown and the simulated lateral electrical field boundary in high resistivity silicon detectors with multi-guard ring structure. IEEE T. Nucl. Sci. 47, 729-736 (2000). https://doi.org/10.1109/23.856506

- 14. X. Lei, X.G. Gao, J. Deng et al., A 15 V-tolerant and radiationhardened MOSFET driver with positive and negative references. IEEE Trans. Aerospace Electr. Syst. 59, 851–857 (2022). https:// doi.org/10.1109/TAES.2022.3191296

- 15. K.G. Aubuchon, H.T. Peterson, D.P. Shumake, Radiation-hardened CMOS/SOS LSI circuits. IEEE T. Nucl. Sci. 23, 1613-1616 (1976). https://doi.org/10.1109/TNS.1976.4328550

- 16. P.E. Dodd, M.R. Shaneyfelt, B.L. Draper et al., Development of a radiation-hardened lateral power MOSFET for POL applications. IEEE T. Nucl. Sci. 56, 3456-3462 (2009). https://doi.org/10.1109/ TNS.2009.2033922

- 17. W. Huang, H.X. Liu, Q. Xu et al., Design of 30 V high-voltage low-power radiation-tolerant analog switch IC. IEEE T. Nucl. Sci. 69, 883-889 (2022). https://doi.org/10.1109/TNS.2022.3151409

- 18. X. Xiang, X.G. Gao, F. Liu et al., A radiation-hardened and ESDoptimized wireline driver with wide terminal common-mode voltage range. IEEE T. Nucl. Sci. 65, 566-572 (2018). https://doi.org/ 10.1109/TNS.2017.2778942

- 19. Y. Wang, R. Hu, R. Li et al., Total dose effects on the matching properties of deep submicron MOS transistors. J. Semicond. 35, 064007 (2014). https://doi.org/10.1088/1674-4926/35/6/064007

- 20. J.A. Schmitz, D. Rogge, S. Balkir et al., A low-power, highly integrated radiation detection system for portable, long-duration

**115** Page 10 of 10 W. Huang et al.

monitoring. IEEE Sens. J. **20**, 10664–10678 (2020). https://doi.org/10.1109/JSEN.2020.2995288

- L. Artola, N.J.H. Roche, G. Hubert et al., Analysis of angular dependence of single-event latchup sensitivity for heavy-ion irradiations of 0.18 μm CMOS technology. IEEE T. Nucl. Sci. 62, 2539–2546 (2015). https://doi.org/10.1109/TNS.2015.2495101

- F. Ravotti, Dosimetry techniques and radiation test facilities for total ionizing dose testing. IEEE T. Nucl. Sci. 65, 1440–1464 (2018). https://doi.org/10.1109/TNS.2018.2829864

- L.Y. Xiao, W.F. Fang, Z.Y. Tian et al., Design and offline testing of a resonant stripline beam position monitor for the IRFEL project at NSRL. Nucl. Sci. Tech. 31, 70 (2020). https://doi.org/10.1007/s41365-020-00778-7

- L. Zhao, Z.Y. Jiang, R.S. Dong et al., An 8-Gs/s 12-Bit TIADC system with real-time broadband mismatch error correction. IEEE T. Nucl. Sci. 65(12), 2892–2900 (2018). https://doi.org/10.1109/TNS.2018.2878875

- W. Zhao, X.Q. Guo, W. Chen et al., Temporal characteristic analysis of single event effects in pulse width modulator. Nucl. Sci. Tech. 28, 29 (2017). https://doi.org/10.1007/s41365-017-0254-3

- V.S. Anashin, P.A. Chubunov, S.A. Iakovlev et al., in 2015 15th European Conference on Radiation and Its Effects on Components and Systems (RADECS) (2015), pp. 1–6. https://doi.org/10.1109/ RADECS.2015.7365691

- J.S. Yun, M. Cui, J.B. Han et al., Determining the effect of relative size of sensor on calibration accuracy of TEM cells. Nucl. Sci. Tech. 30, 98 (2019). https://doi.org/10.1007/s41365-019-0618-y

- W. Huan, Z. Chen, Compensation method for the coupling error between the EUT and TEM cell in E-field probe isotropic calibration. 2015 IEEE ISEMC, 1195–1200 (2015). https://doi.org/10. 1109/ISEMC.2015.7256339

- X.L. Qian, J.F. Chang, C.F. Feng et al., Calibration of pulse transit time through a cable for EAS experiments. Chin. Phys. C 38, 066202 (2014). https://doi.org/10.1088/1674-1137/38/6/066202

- X.L. Qian, H.Y. Sun, C. Liu et al., Simulation study on performance optimization of a prototype scintillation detector for the GRANDProto35 experiment. Nucl. Sci. Tech. 32, 51 (2021). https://doi.org/10.1007/s41365-021-00882-2

- Q.Q. Cheng, Y.Y. Zhong, C.W. Ma et al., Gamma measurement based on CMOS sensor and ARM microcontroller. Nucl. Sci. Tech. 28, 122 (2017). https://doi.org/10.1007/s41365-017-0276-x

- X.L. Qian, X. Wang, H.Y. Sun et al., Simulation study on cosmic ray background at large zenith angle based on GRAND Proto 35 coincidence array experiment. Nucl. Sci. Tech. 32, 5 (2021). https://doi.org/10.1007/s41365-020-00841-3

- D.W. Lane, X-ray imaging and spectroscopy using low cost COTS CMOS sensors. Nucl. Instrum. Methods Phys. B 248, 29–32 (2012). https://doi.org/10.1016/j.nimb.2011.09.007

- L.X. Yi, Q.K. Yi, C.Q. Zhi et al., Simulation of gamma minitype reference radiation for calibration of personal dosimeter. Nucl. Sci. Tech. 31, 12 (2020). https://doi.org/10.1007/s41365-019-0715-y

- Y. Xu, B. Wei, B.J. Mao et al., Shielding research of minitype reference radiation device based on Monte Carlo simulation. High Power Laser Part. Beams 28, 168–175 (2016). https://doi.org/10. 11884/HPLPB201628.160018 (in Chinese)

- W.J. Li, Y.X. Liu, B. Wei et al., Monte Carlo simulation investigation on the minitype reference radiation employed for the calibration on gamma ray dose or dose rate meters. J. Radiol. Prot 38, 407–421 (2018). https://doi.org/10.1088/1361-6498/aa9fb9

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.