# Design and prototyping of the readout electronics for the transition radiation detector in the high energy cosmic radiation detection facility

Jie-Yu Zhu<sup>1,2</sup> • Yang-Zhou Su<sup>1,2</sup> • Hai-Bo Yang<sup>1,2</sup> • Fen-Hua Lu<sup>1,2</sup> • Yan Yang<sup>3</sup> • Xi-Wen Liu<sup>3</sup> • Ping Wei<sup>3</sup> • Shu-Cai Wan<sup>1,2</sup> • Hao-Qing Xie<sup>1</sup> • Xian-Qin Li<sup>1,2</sup> • Cong Dai<sup>3</sup> • Hui-Jun Hu<sup>3</sup> • Hong-Bang Liu<sup>3</sup> • Shu-Wen Tang<sup>1,2</sup> • Cheng-Xin Zhao<sup>1,2</sup>

Received: 8 November 2023 / Revised: 12 January 2024 / Accepted: 7 February 2024 / Published online: 24 May 2024 © The Author(s), under exclusive licence to China Science Publishing & Media Ltd. (Science Press), Shanghai Institute of Applied Physics, the Chinese Academy of Sciences, Chinese Nuclear Society 2024

## Abstract

The high energy cosmic-radiation detection (HERD) facility is planned to launch in 2027 and scheduled to be installed on the China Space Station. It serves as a dark matter particle detector, a cosmic ray instrument, and an observatory for high-energy gamma rays. A transition radiation detector placed on one of its lateral sides serves dual purpose, (i) calibrating HERD's electromagnetic calorimeter in the TeV energy range, and (ii) serving as an independent detector for high-energy gamma rays. In this paper, the prototype readout electronics design of the transition radiation detector is demonstrated, which aims to accurately measure the charge of the anodes using the SAMPA application specific integrated circuit chip. The electronic performance of the prototype system is evaluated in terms of noise, linearity, and resolution. Through the presented design, each electronic channel can achieve a dynamic range of 0–100 fC, the RMS noise level not exceeding 0.15 fC, and the integral nonlinearity was <0.2%. To further verify the readout electronic performance, a joint test with the detector was carried out, and the results show that the prototype system can satisfy the requirements of the detector's scientific goals.

**Keywords** HERD  $\cdot$  Dark matter particle detection  $\cdot$  TRD  $\cdot$  Readout electronics  $\cdot$  SAMPA  $\cdot$  Data acquisition  $\cdot$  Performance test

This work was supported by the National Natural Science Foundation of China (Nos. 12375193, 11975292, 11875304), the CAS "Light of West China" Program, the Scientific Instrument Developing Project of the Chinese Academy of Sciences (No. GJJSTD20210009), the CAS Pioneer Hundred Talent Program.

Hai-Bo Yang yanghaibo@impcas.ac.cn

- <sup>1</sup> Institute of Modern Physics, Chinese Academy of Sciences, Lanzhou 730000, China

- <sup>2</sup> School of Nuclear Science and Technology, University of Chinese Academy of Sciences, Beijing 100049, China

- <sup>3</sup> Guangxi Key Laboratory for Relativistic Astrophysics, School of Physical Science and Technology, Guangxi University, Nanning 530004, China

# **1** Introduction

Dark matter [1], cosmic rays [2], and high-energy gamma rays [3] are the particles of interest in physics and cosmology research. To detect the existence of dark matter and explore the origin of cosmic radiation, many experimental devices have been launched into space, including FERMI [4], AMS [5], CALET [6], CREAM [7], and JEM-EUSO [8]. China's first scientific experimental astrophysics satellite, the Dark Matter Particle Explorer (DAMPE), was launched on 17th of December, 2015, marking the beginning of China's space-borne dark matter space exploration [9–15]. Although these devices have made outstanding scientific discoveries, there is still much exploration left to prove the existence of dark matter particles and gain deeper insights on the origin of the universe.

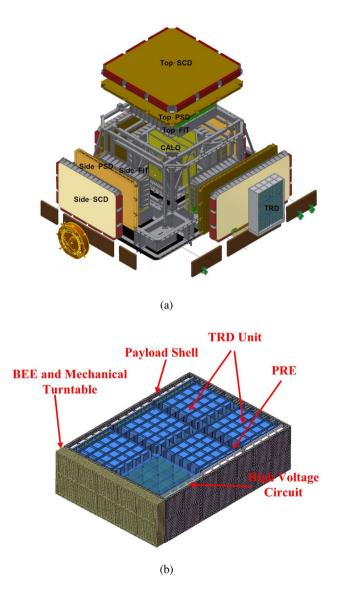

To improve the ability to detect dark matter and cosmic rays in space, the High Energy Cosmic-Radiation Detection (HERD) project has been proposed by scientists [16, 17]. HERD will be installed on the China Space Station in 2027, with the scientific goals of detecting dark matter, precision cosmic ray spectrum, and composition measurement [18]. Figure 1a illustrates HERD's architecture, which consists of five detector systems: an electromagnetic calorimeter (CALO), the fiber tracker (FIT), a plastic scintillator detector (PSD), a silicon charge detector (SCD), and a transition radiation detector (TRD). The HERD is expected to operate on the space station for a decade [19]. The HERD can detect electron / photon with an energy range of 10 GeV–100 TeV/0.5 GeV–100 TeV ( $e/\gamma$ ); its primary cosmic ray nucleus detection range can reach 30 GeV–3 PeV; its energy resolution can reach 1% at 200 GeV(e) and 20% at 100 GeV-PeV(p). These performance indicators are superior to those of contemporary space devices in operation [20–22]. For

Fig. 1 (Color online) a Structure of the HERD payloads. b TRD configuration

instance, HERD's instruments will extend the cosmic ray nuclear detection range by an order of magnitude and the nucleon energy resolution will be doubled compared to DAMPE; while compared to the FERMI satellite, HERD has higher sensitivity and a larger detection geometry factor. Thus, HERD is expected to produce essential research results during its operational lifetime.

The TRD is one of HERD's major subsystems and its primary scientific goal is to perform the absolute energy calibration of the CALO in the TeV energy range. The calibration operation will be carried out once in every 3-6 months, during which a mechanical turntable will rotate the TRD into the field of view of the CALO. The analysis of cosmic-ray proton events co-triggering the CALO and the TRD allows the transition radiation (TR) response of the TRD to be calibrated using the ground electron beam's TR calibration curve and consequently the CALO's absolute energy calibration. The calibration accuracy is expected to reach 10%. When the calibration is completed, the mechanical turntable will rotate the TRD out of the field of view of the CALO, and the TRD will be switched to the autonomous observation mode to perform gamma-burst observation and independent astronomical X-ray observations [23]. High-energy charged particles will enter the detector from the front and will be first converted into TR photons by the radiator, and then enter a gas detection cavity to realize the detection of TR photon signals. As shown in Fig. 1b, the TRD consists of TRD detection units, readout electronics, a high voltage circuit, and its mechanical structure. The dimensions of the TRD are 650 mm (L)  $\times$  900 mm (W)  $\times$ 250 mm(H), with a total weight less than 150 kg. The readout electronics of each unit are mounted on its side. The TRD detection unit consists of a regular radiator and a gas detector. Due to the limitation of the regular radiator area and the thickness of the drift region, the TRD cannot be designed as a single module. The complete TRD has six units arranged in a 3 rows and 2 column format. The signal from the detector will be read out via an anode, with a charge dynamic range of 100 fC. To guarantee the accuracy of detector measurements, the readout electronics system must exhibit an integral nonlinearity of less than 2% and maintain a noise level of less than 3 fC. Therefore, the electronics design is a challenge.

Conventional design of readout electronics generally uses either discrete components or application specific integrated circuit (ASIC) chips. However, there are strict constraints on board integration and power consumption in space-borne devices. Therefore, ASIC chips are more commonly adopted for these applications. Most of the commonly-used ASIC chips suitable for TRD dynamic range adopt designs such as APV25 [24], PASA+TRAP [25], SPADIC [26], AGET [27], and SAMPA [28, 29]. After research, the SAMPA's ASIC chip was selected as the optimal choice for the TRD's readout electronics. Beacuse this chip's radiation resistance has been tested and it is proven to meet space operational requirements [30]. The SAMPA chip is a digital-analog hybrid ASIC with 32 channels and three dynamic ranges, namely 67 fC, 100 fC, and 500 fC. The power consumption of the CAS+ shaper of SAMPA is less than 8 mW, and the power consumption of its analog-to-digital converter (ADC) is 2 mW at 10 MSPS. In addition, a modular design with triple redundancy is adopted so that the chip can operate in space radiation environments.

A TRD detector prototype was developed with 64 readout channels. Therefore, two SAMPA chips will be needed for the TRD prototype's readout electronics. In this paper, the design and development of the prototype's readout electronics (PRE) for the TRD are discussed. In addition, the performance of the PRE was analyzed experimentally and a joint debugging experiment was carried out with the detector. The research results will discuss the suitability of the proposed PRE to HERD-TRD's designs.

## 2 Hardware design of the PRE

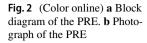

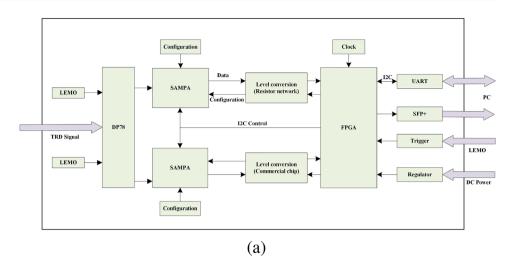

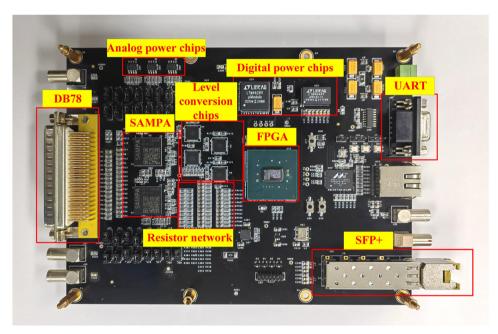

The PRE requirements for space applications differ from those of ground-based systems. Due to the complex operational environment, the space station's power consumption and hardware limitations, the front-end electronics require high speed, low power consumption, and high noise and radiation tolerance. Readout electronics for space-borne systems are expensive to produce, so it is necessary to design the prototypes first and validate the functionality of the design. The PRE uses the analog-digital mixed-mode ASIC chip, SAMPA to achieve low noise levels, highly reliable charge measurements, and digital-to-analog conversion. Moreover, the zero-suppression function integrated into SAMPA can realize data compression and decrease the transmission bandwidth. For the PRE, two SAMPA chips were used to realize 64 channels of detector signal readout. Figure 2 shows the block diagram and photograph of the PRE, which includes the SAMPA circuit, a scalable lowvoltage signaling (SLVS) and low-voltage differential signaling (LVDS) level conversion circuit, a field-programmable gate array (FPGA) circuit, the power management circuit, the communication interface circuit, and the detector signal interface circuit. The PRE uses a Xilinx Kintex7 XC7K70T-2FBG676I FPGA for control and data transmission [31]. The charge pulse signal generated by the detector is connected to the DB78 connector of the PRE through an interface board. The charge signal is integrated, shaped, and digitized at 10 MSPS in the SAMPA chip and the data are sent to the level conversion circuit at a frequency of 320 MHz. The FPGA receives the data from the level conversion circuit, processes and packages it, and transmits it to a host computer through a Gigabit Ethernet link. In addition, the PRE can receive control commands and transmit parameter information to the host computer through a universal asynchronous receiver/ transmitter (UART) interface. Through the UART interface, the PRE can be configured to operate in raw data or zerosuppression mode, and a series of tests were conducted in both modes to validate the system's operation.

## 2.1 SAMPA ASIC

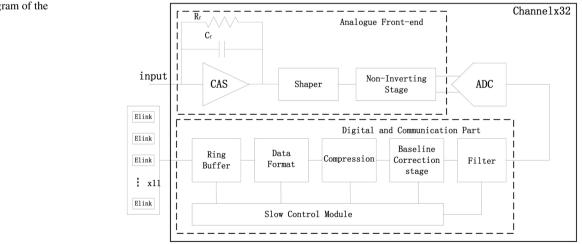

The SAMPA is a large-scale analog-digital hybrid ASIC designed by CERN for the upgraded front-end electronics system of the Time Projection Chamber (TPC) and Muon Chambers (MCH) in the ALICE experiment. SAMPA has good robustness to radiation and is suitable for radiated environments. A single SAMPA chip has 32 channels, and up to 11 data links can be selected for readout. The SAMPA structure is shown in Fig. 3. The chip is split into analog and digital signal processing subsystems, which are connected through an ADC.

The analog part mainly includes a positive/negative polarity charge-sensitive amplifier (CSA), a semi-Gaussian pulse shaper module, and a non-inverting stage. The feedback mechanism of the CSA consists of the capacitive feedback  $C_{\rm f}$  and the resistive feedback  $R_{\rm f}$  in parallel, and the amplified voltage signal is transmitted to the semi-Gaussian pulse shaper module for further processing. The shaper module includes a high-pass filter and two bridged-T second-order low-pass filters that produce a 4th-order semi-Gaussian pulse. Internal registers are used to set the amplifier gain to 4 mV/fC, or 20 mV/fC, or 30 mV/fC. The shaping time settings available are 160 ns and 300 ns. Then, the shaper signal is digitized using a successive-approximation ADC, which can operate at sampling rates of 10 MHz or 20 MHz. The digital signal processor (DSP) section contains different digital filters, including three baseline correction modules, a tail cancelation module, and a data compression module. The DSP will package the data processed by the SAMPA chip and facilitate data extraction and verification through a 50-bit packet header [32]. SAMPA has 40 global registers and 30 channel registers (only accessible through the global register), which can be controlled through the interintegrated circuit (I2C) bus protocol to configure the main functions of the chip or channels.

## 2.2 Level conversion circuit

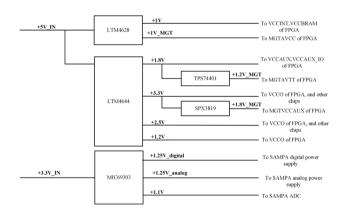

The serial communication link uniformly employs SLVS level conversion circuit, which includes 11 high speed differential data links, with clock and trigger links. SLVS is a special form of LVDS, with a lower common mode voltage (200 mV) and voltage swing (200 mV). The use of SLVS standard levels allows the SAMPA chip to reduce its power

consumption. However, many FPGA chips do not support the SLVS standard, so SLVS and LVDS level conversion are required to communicate link data to the FPGA and provide SAMPA configuration information. For this purpose, two methods were adopted, namely an industrial conversion chip and a resistor network.

The commercially-available industrial chip method uses the MC20901 and MC20902 level conversion chips to achieve SLVS to LVDS matching and vice-versa. Both chips are high-performance bridge chips for FPGA that can achieve level matching of five signals on a single chip, supporting data rates up to 2.5 Gbps. On the other hand, resistor networks can achieve the same performance as that of the commercial chips. The resistance network is shown in Fig. 4, where Fig. 4a shows the conversion mechanism from SLVS to LVDS for communicating SAMPA data to the FPGA, while the circuit Fig. 4b performs the opposite function. These networks are more resistant to radiation than commercial chips and have lower cost and power consumption. Therefore, resistor networks are adapted for future implementations instead of commercial chips.

## 2.3 Interface circuit

The TRD is a sealed gas detector and has strict sealing requirements. For the PRE implementation, a ceramicencapsulated DB78 connector is adopted for signal transmission, and a PCB board-mounted connector is used on the PRE side. Aadditionally, to test the electronics performance, four standard LEMO connectors are used to lead out the four input signals of the SAMPA chip.

A highly reliable communication interface connection is required between the PRE and the host computer. The PRE's configuration commands downstream and status parameters upstream are transmitted through a UART interface operating in full-duplex mode. The scientific data transfer interface is designed to use a small form-factor pluggable (SFP) connector. The differential inputs and outputs of the SFP interface are directly connected to the FPGA's GTX. Connection

Fig. 4 Resistance networks for signal level conversion. a SLVS to LVDS level conversion. b LVDS to SLVS level conversion

to the host computer is via a 1000BASE-T SFP transceiver module and a Category 6 cable through the SiTCP network protocol processor. SiTCP is a hardware-based TCP processor for front-end readout electronics intended for applications where hardware space is limited [33], and can handle TCP, IP, and Ethernet protocols for data transmission.

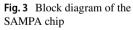

## 2.4 Power supply circuit

To ensure the consistent operation of the PRE, a stable power supply is necessary. The board requires two power supplies, namely a 5 V and a 3.3 V supply, which are provided by an external power source. A set of power regulators provides the power required for the SAMPA, FPGA, and other onboard components. The lower supply voltages for the SAMPA are generated through low-noise linear regulators together with LC filter circuitry. Figure 5 shows the power distribution architecture of the FPGA, SAMPA, and other chips. The Xilinx FPGA requires power for its power-on sequence. In the case of the PRE, power rails are designed to meet this requirement. The PGOOD pin of the DC-DC power supply is cascaded to the "Enable" pin of the subsequent power supply to complete the power-on sequence of the power supply. The power-on time is at most 50 ms

Fig. 5 Block diagram of the SAMPA power distribution circuit

according to the manufacturer, so a capacitor was added to the ground on the TRACK/SS pin to reduce the poweron time. The analog and digital circuits also contain two grounds, AGND and DGND, which are directly connected to the dedicated ground plane of the PCB. These designs ensure the stability of the PRE power supply.

## **3 PRE firmware function**

The firmware functions of the PRE are implemented through its Xilinx Kintex-7 FPGA, which performs board control and data transmission. The two key functions of the PRE firmware are (i) to provide configuration and readout of internal registers, clocks and trigger signals for the two SAMPA chips, and (ii) to identify and package the detector-scientific data packets from SAMPA and pass them through the Gigabit Ethernet to the host computer. As shown in Fig. 6, the firmware function is divided into a command configuration unit, a data processing unit and a data transmission unit, which are analyzed further.

## 3.1 SAMPA configuration unit

The SAMPA configuration unit is divided into three modules: the Clock Part, the Config Part, and the Trigger Part. The Clock Part is responsible for providing the system clock which is required for the entire firmware system operations and the SAMPA operating clock. SAMPA has a number of global and channel registers. Certain aspects of SAMPA's configuration and status can be controlled through these registers. The global registers can be directly controlled through the I2C interface, which is mainly responsible for configuring the key functions and status of SAMPA. Additionally, these registers can also set the configuration that is common to all channels. The channel registers available on each channel enable specific configurations of individual channels and can only be controlled through global registers. The Config Part transmits the configuration commands sent by the host

SAMPA Feedba PC Config Part Trigger Part Clock Part SAMPA Configuration Data Data SITCP SAMPA Send\_con Control Part SAMPA configuration unit Data transmission unit SAMPA Data Packet Data Data STD Data receive Data packet FIFO Part Part Part Data processing uni

Fig. 6 Block diagram of FPGA logic design

computer to the IIC processing unit through the UART bus interface, packages them according to the protocol, sends them to the global registers inside SAMPA, and transmits the returned values to the host computer. SAMPA has two operating modes, namely an external triggering mode and an internal triggering mode. In the external triggering mode, the Trigger Part module will feed external trigger signals that meet the requirements into SAMPA, and the trigger signal will act as a data transmission control signal in the data transmission unit.

#### 3.2 Data processing unit

SAMPA is a hybrid digital-analog chip with eleven digital signal serial transmission links capable of operating at 80 Mbps or 160 Mbps or 320 Mbps, which transmit the data stream to the data processing part. The data processing unit is responsible for acquiring the digital signal transmitted by SAMPA, analyze them to determine their header and tail portions. The unit determines the signal validity, package, process, and send the same to the data transmission module. In the design, the SAMPA operating clock is designed as a high-speed clock of 320 MHz, but it does not provide a data reference clock; therefore, high-speed signal acquisition at 320 Mbps is a challenge.

The data stream from the SAMPA to the FPGA uses double-edge sampling, and the phase between the data and the clock is calibrated through the internal IDDR and IODELAY parameters to avoid missing the setup and hold timings. To facilitate data alignment, the SAMPA chip generates synchronous signal packets with higher priority than data packets on each link under idle or mandatory commands. The sync signal is set by identifying the SAMPA internal sync packet, and the edge is replaced when the sync signal is pulled low. The edge changes only once because repeated changes do not solve the metastability problem. The synchronized data are passed to the subsequent Data\_receive Part module. This module identifies the serial data, find the header and tail parts of the packet, filter out the synchronization packet and empty packets (if present). The data are converted into a 10-bit data transmission form for the Data\_packet Part. The latter will then pack the 10-bit data into 64-bit packets and insert flag bits to identify their headers, tails and FIFO overflow parts to facilitate the subsequent data analysis. The final 64-bit data packets are transmitted to the following Data transmission module through the FIFO circuit.

### 3.3 Data transmission unit

The key functions of the data transmission unit are data summary and SiTCP transmission. These functions are mainly realized through two modules, Send\_con Part and Data\_SITCP Part. The data stream of all channels of SAMPA can be read from links 1–11 by configuring the internal registers. However, the peripheral circuits will become more complex as the transmission link increases, and the resultant power consumption of the circuit increases. Therefore, selecting the number of transmission links needs to consider the triggering rate, the transmission speed, and overall power consumption.

To achieve stable data reading in the external trigger mode at rates above 1 kHz and reduce the power consumption of the FPGA as much as possible, four links are used to read a chip, and each link carries eight data channels. The 320 Mbps high-speed data link aggregation was also an issue in the design. To solve this problem, a gatekeeper module was designed that generates a data transmission flag after the time window ends by delaying the trigger signal. This allows controlling the transfer window at a specific time and switching the transmission channel through the empty and full signals of the FIFO of each link in the Data processing unit. The FIFO's empty signal is monitored sequentially to ensure uninterrupted sequential readout. The readout data are aggregated into a deeper summary FIFO queue and then transmitted across clock domains to the SITCP transmission module, and finally to the host computer through the Gigabit Ethernet link.

## 4 Performance measurements

To explore whether the PRE design can meet the application requirements of the TRD, a series of tests was performed using the PRE's raw data and zero-suppression modes. These included a baseline characterization test, a channel linearity test, an amplitude resolution test, a crosstalk test, a long-term operational stability test, an equivalent noise level test under different input signals, and a joint detector test. The test results were analyzed to evaluate the performance of PRE and verify the reliability of the design. For the tests, the SAMPA was configured to operate at 320 MHz clock rate, the ADC sampling clock was set to 10 MHz, the internal charge-sensitive preamplifier gain was set to 20 mV/fC, the shaping time was set to 160 ns, and the negative charge is collected. The test input pulse signal and trigger were generated using a signal generator (Tektronix AFG31000). The pulse signal output simulated the charge signal generated by the detector pad. During the test, voltage-to-charge conversion was realized using a charge converter board. A bank of sixty-four capacitors of 1 pF each is placed on the charge converter board to convert the voltage pulses from the signal source to charge signals, which were then input to the analog pins of the SAMPA through the DB78 connector for testing. The input test signal was set up as a negative polarity pulse signal with a rising edge of 30  $\mu$ s, a falling edge of 2 ns, a pulse width of 50  $\mu$ s, and a voltage range of 0–100 mV; this resulted in a charge ( $Q = C \times V$ ) being injected through the capacitor to generate a charge signal of 0–100 fC. The trigger signal was a square wave with an amplitude of 3.3 V and a pulse width of 200  $\mu$ s. The input pulse signal is delayed by 10  $\mu$ s from the trigger signal to prevent incomplete signal acquisition.

### 4.1 Baseline noise characterization

Noise characterization refers to the modeling of the random perturbations introduced during the signal transmission and processing, and is of great significance for interpreting experimental results, electronic model verification, and physical information extraction. Baseline noise testing is used to quantify system noise levels and evaluate the reliability of electronic data. To avoid the undershoot phenomenon at the trailing edge of the pulse signal, which could affect the regular operation of the SAMPA's DSP module, the input signal of SAMPA was superimposed on the baseline level in the analog front end.

During the test, a baseline noise analysis of the 64 channels of the two SAMPA chips of the PRE was carried out. The acquisition time window was 10  $\mu$ s, with a trigger frequency of 1 kHz. This was aimed to simulate the state of the TRD detector when it is in orbit during the calibration of the electromagnetic Calorimeter and the transmission of uncompressed raw data. The level of noise was characterized through its Root Mean Square (RMS) value.

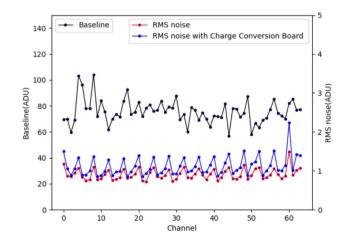

Figure 7 illustrates the baseline data and corresponding RMS noise levels. The black line represents the baseline levels, which were in the range of 60–110 ADC codes. The red line represents the RMS noise of the electronics, and the blue line represents the change in RMS noise with the addition of the charge conversion board. The acquisition time for each test was one minute. From Fig. 7, it can be seen that connecting the

Fig. 7 (Color online) Baseline and RMS noise levels of the PRE

charge conversion board to the PRE will introduce some noise. The RMS noise of the PRE is below 1.5 ADC code (which is equivalent to 0.15 fC), and is increased to less than 2.5 ADC code (equivalent to 0.24 fC) after the board is connected. Due to the limited space for installing electronics in the space station, the charge conversion board or cable will be connected between the PRE and the detector to achieve a more compact configuration. This indicates that the future adapter board or cable designs should focus on reducing the noise introduced.

## 4.2 Channel linearity test

Ideally, the relationship between the input and output of a readout electronics system is a linear function of positive proportion, whose slope represents the magnification of the readout system. Integral nonlinearity refers to the nonlinear distortion introduced by the channel during the integration of the input signal, and this distortion can be used to evaluate the linearity of a readout electronics system.

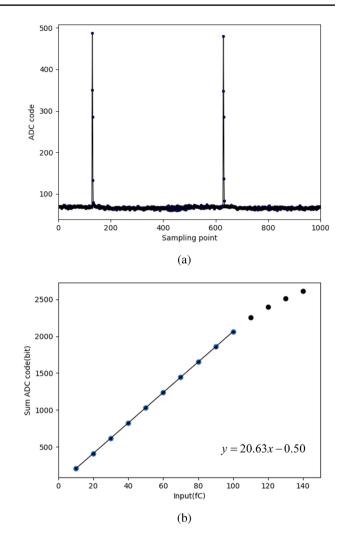

A voltage pulse was generated using the pulse signal generator and sent to the charge conversion board to generate charges of 0–100 fC in steps of 10 fC. The PRE was set to operate in zero-suppression mode with the threshold set to 10 ADC codes beyond the baseline, at a trigger frequency of 1 kHz and a sampling time window of 100  $\mu$ s. Due to the limited transmission bandwidth available at the space station, waveform accumulation, compression and peak finding may be required on the waveform obtained by each channel. After accumulation, the waveform's linear expression is fitted to calculate the integral nonlinearity. Figure 8a shows the waveform of the acquired input at 50 fC, while Fig. 8b shows a randomlyselected channel, whose integral nonlinearity was 0.16%.

#### 4.3 Amplitude resolution test

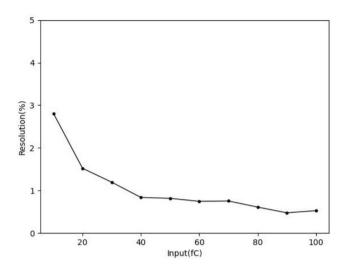

Amplitude resolution indicates the electronics system's ability to resolve different input signal amplitudes and equivalently characterizes the energy resolution for the system. The TRD will use the linear relationship between the cross-radiation response of charged particles and the Lorentz factor to perform absolute energy calibration of the electromagnetic calorimeter in orbit, so it requires the readout system with high-precision energy resolution.

For this test, the input charge was set in the range of 0-100 fC in steps of 10 fC. Waveform fitting was performed using the 4th order semi-Gaussian pulse to obtain the amplitude resolution curve of the PRE as [34],

$$f(x) = a\left(\frac{x-t}{\tau}\right)e^{-N(\frac{x-t}{\tau})} + Bl,$$

(1)

where N is the shaping order, which is set to 4,  $\tau$  is the peak time, *Bl* is the baseline, *t* is the start time and  $Ae^{-4}$  is the amplitude.

Fig. 8 a Output waveform for a 50 fC input signal and b linearity test results of the PRE

Figure 9 shows the amplitude resolution of the PRE at different input amplitudes where the resolution of the system after 10 fC is better than 3%.

## 4.4 Equivalent noise level test under different input signals

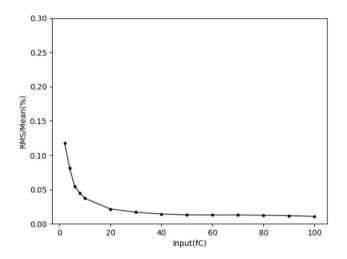

A 2–10 fC charge signal was generated using the signal source at a step of 2 fC and a 20–100 fC signal at a step of 10 fC. A scan test was conducted to observe the equivalent noise level (ENL) change under different input charges. The frequency of the input signal was set to 1 kHz. The SAMPA gain was set to 20 mV/fC in the test, and each charge value was tested in zero-suppression mode for one minute. The RMS value represents the ENL of the PRE. Figure 10 shows the ENL curve of a PRE channel. The amount of input charge is presented on *x*-axis, while the *y*-axis shows the RMS percentage compared to the measured mean value. It

Fig. 9 Amplitude resolution of the PRE

Fig. 10 The ENL test under different input charge

can be observed from the figure that the relative noise level tends to decrease as the input signal increases.

## 4.5 Crosstalk test

The channel-to-channel crosstalk in a readout electronics system represents the interference effect of a channel on the signal to its adjacent channels. Crosstalk will introduce additional noise during signal transmission and measurement, thus affecting the signal quality and possibly causing distortion and measurement errors. During the test, a single SAMPA channel was injected with a charge, while the remaining channels were left floating. The input pulse signal is 100 mV, and its equivalent input charge is 100 fC, the maximum input range at a gain of 20 mV/fC of the SAMPA. After calculation, the crosstalk coefficients of the

Fig. 11 Stability test of the PRE channel over long-term operation

adjacent channels were 0.023% and 0.011%, which show that the impact of crosstalk was negligible.

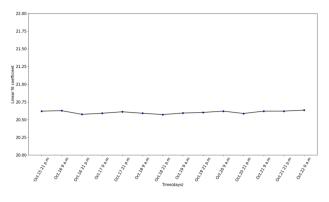

#### 4.6 Data reading stability test

A data reading stability test system was set up to demonstrate the reliability of data transmission and interconnection using the PRE, a signal source and a host computer. The frequency of the signal source was set to 1 kHz. To perform this test, the system was operated in zero-suppression mode for one week, and a linearity test was performed every day at 9 a.m. and 9 p.m. In the offline data analysis, the test data were linearly fitted using a first-order linear fit coefficient to determine the stability of the gain. Figure 11 shows the coefficients of the linear fit over time for one SAMPA channel, and it can be seen that the gain is relatively stable. The entire system operated stably without any data packet loss.

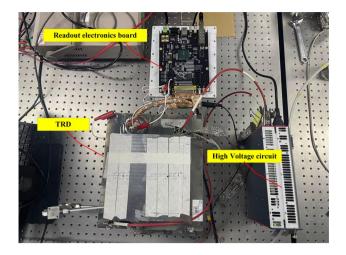

## 4.7 Joint test with TRD

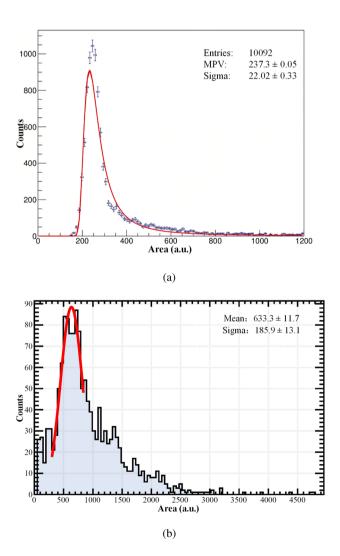

To verify the performance of the PRE design, conducting a joint test with the TRD was necessary. Internally, the working gas of the TRD was 97%Ar + 3%C<sub>4</sub>H<sub>10</sub>. The experimental platform was built as shown in Fig. 12. The test system included the PRE, a TRD, a high-voltage power supply, a low-noise digital power supply and a host computer. During the test, cosmic rays were used to test and verify the system at first. Then, a <sup>55</sup>Fe radioactive source was used for testing. In the cosmic ray test, the external trigger signal for the electronic system is generated using a plastic scintillation detector (PSD) which is then fed to the PRE. Figure 13a shows the cosmic ray energy spectrum of the TRD, which conforms to the Landau distribution. Figure 13b shows the <sup>55</sup>Fe energy spectrum when a high voltage of 6200 V was applied to the detector cathode and a high voltage of 1800 V was applied to the thick gaseous electron multiplier (THGEM). For this test, the SAMPA chip is configured in the self-triggered mode with a sampling time window of 100  $\mu$ s. The gain of the SAMPA chip was 20 mV/fC. The

Fig. 12 (Color online) Experimental platform of joint test with TRD

Fig. 13 a Energy spectrum with cosmic ray. b Energy spectrum with  $^{55}$ Fe radioactive source

measured energy resolution of signal integral is 29.3% for full-energy peak (5.9 keV energy). The peak of the cosmic ray is approximately one-third of the <sup>55</sup>Fe full-energy peak. The test demonstrates the feasibility of applying the SAMPA chip to TRD, and the designed TRD prototype readout electronics system achieved its intended purpose.

## 5 Conclusion

In this paper, a PRE design suitable as the TRD detector for the HERD project of the China Space Station is proposed and validated. This PRE has 64 channels and a total power consumption of 6.26 W. The PRE mainly consists of a detector interface circuit, a SAMPA chip and its peripheral circuits, SLVS and LVDS level conversion circuits, an FPGA circuit, a power management circuit, and a communication interface circuit. The tests performed indicate that the PRE system performed well. The baseline noise level of the 64 channels is low, with the RMS noise level being less than 1.5 ADC code, which accounts to only 0.15% of the dynamic range of the PRE. The integral nonlinearity of the channel was less than 0.2%, and moreover, the amplitude resolution also meets the design requirements. To further verify the performance of the PRE, it is coupled to the TRD. The results from the cosmic ray test serve as evidence that the PRE is functioning effectively. Energy resolution of 29.3% is obtained with a <sup>55</sup>Fe radioactive source for 5.9 keV energy. According to this, the PRE design can meet the needs of TRD readout and can constitute a basis for future engineering design of relevant systems.

**Acknowledgements** The authors would like to thank all members of the HERD Collaboration for supporting this work.

Author contributions All authors contributed to the study conception and design. Material preparation, data collection, and analysis were performed by Jie-Yu Zhu, Yang-Zhou Su, Hai-Bo Yang, Fen-Hua Lu, Yan Yang, Xi-Wen Liu, Ping Wei, Shu-Cai Wan, Hao-Qing Xie, Xian-Qin Li, Hui-Jun Hu, Hong-Bang Liu, Shu-Wen Tang and Cheng-Xin Zhao. The first draft of the manuscript was written by Hai-Bo Yang, and all authors commented on versions of the manuscript. All authors have read and approved the final manuscript.

**Data availibility** The data that support the findings of this study are openly available in Science Data Bank at https://cstr.cn/31253.11.sciencedb.j00186.00474 and https://www.doi.org/10.57760/sciencedb.j00186.00474.

#### Declarations

**Conflict of interest** Cheng-Xin Zhao is an editorial board member for Nuclear Science and Techniques and was not involved in the editorial review, or the decision to publish this article. All authors declare that there are no Conflict of interest.

# References

- 1. Y. Bai, Dark matter is darker. Nucl. Sci. Tech. 34, 81 (2023). https://doi.org/10.1007/s41365-023-01249-5

- H. Wang, D. Wang, R. Chen et al., Electronics system for the cosmic X-ray polarization detector. Nucl. Sci. Tech. 34, 64 (2023). https://doi.org/10.1007/s41365-023-01221-3

- X.M. Liu, S.W. Tang, W. Wang et al., Simulation of a soft-gammaray polarimeter on board a microsatellite. Nucl. Sci. Tech. 34, 166 (2023). https://doi.org/10.1007/s41365-023-01303-2

- A.A. Abdo, M. Ackermann, M. Ajello et al., Measurement of the cosmic ray e<sup>+</sup> + e<sup>-</sup> spectrum from 20 GeV to 1 TeV with the fermi large area telescope. Phys. Rev. Lett. **102**, 181101 (2009). https:// doi.org/10.1103/PhysRevLett.102.181101

- M. Aguilar, L.A. Cavasonza, M.S. Allen et al., Properties of iron primary cosmic rays: results from the alpha magnetic spectrometer. Phys. Rev. Lett. 126, 041104 (2021). https://doi.org/10.1103/ PhysRevLett.126.041104

- O. Adriani, Y. Akaike, K. Asano et al., Observation of spectral structures in the flux of cosmic-ray protons from 50 GeV to 60 TeV with the calorimetric electron telescope on the international space station. Phys. Rev. Lett. **129**, 101102 (2022). https://doi.org/ 10.1103/PhysRevLett.129.101102

- E.S. Seo, H.S. Ahn, J.J. Beatty et al., Cosmic-ray energetics and mass (CREAM) balloon project. Adv. Space Res. 33, 1777–1785 (2004). https://doi.org/10.1016/j.asr.2003.05.019

- The JEM-EUSO Collaboration, J.H. Adams, S. Ahmad, et al., The JEM-EUSO instrument. Exp. Astron. 40, 19–44 (2015). https:// doi.org/10.1007/s10686-014-9418-x

- J. Chang, G. Ambrosi, Q. An et al., The DArk matter particle explorer mission. Astropart. Phys. 95, 6–24 (2017). https://doi. org/10.1016/j.astropartphys.2017.08.005

- Y. Zhou, Z.Y. Sun, Y.H. Yu et al., A versatile test bench for photomultiplier tube characterization and its application in the DAMPE-PSD. Nucl. Sci. Tech. 27, 70 (2016). https://doi.org/10. 1007/s41365-016-0072-z

- J.B. Zhang, C.Q. Feng, S.Y. Ma et al., Readout system for groundbased tests of BGO calorimeter of DAMPE satellite. Nucl. Sci. Tech. 28, 143 (2017). https://doi.org/10.1007/s41365-017-0297-5

- H.B. Yang, X.Q. Li, Y.H. Yu et al., Design and evaluation of prototype readout electronics for nuclide detector in very large area space telescope. Nucl. Sci. Tech. 33, 65 (2022). https://doi. org/10.1007/s41365-022-01047-5

- Q. Wan, J.H. Guo, X. Xu. et al., Design of a high-dynamic-range prototype readout system for VLAST calorimeter. Nucl. Sci. Tech. 34, 149 (2023). https://doi.org/10.1007/s41365-023-01291-3

- R. He, X.Y. Niu, Y. Wang et al., Advances in nuclear detection and readout techniques. Nucl. Sci. Tech. 34, 205 (2023). https:// doi.org/10.1007/s41365-023-01359-0

- Y.J. Zhang, Y.H. Yu, Y. Zhou, et al., Development of a test bench for plastic scintillator counters for the DAMPE. Nucl. Tech. 38, 080403 (2015).https://doi.org/10.11889/j.0253-3219.2015.hjs.38. 080403 (in Chinese)

- S.N. Zhang, O. Adriani, S. Albergo et al., The high energy cosmicradiation detection (HERD) facility onboard China's Space Station. In Proceedings of SPIE 9144, Space Telescopes and Instrumentation 2014: Ultraviolet to Gamma Ray, 31 July 2014. https:// doi.org/10.1117/12.2055280

- M. Xu, The high energy cosmic radiation facility onboard China's Space Station. Nucl. Part. Phys. Proc. 279–281, 161–165 (2016). https://doi.org/10.1016/j.nuclphysbps.2016.10.023

- D. Kyratzis, H.E.R.D. Collaboration, Overview of the HERD space mission. Physica Scripta. 97, 054010 (2022). https://doi. org/10.1088/1402-4896/ac63fc

- D. Kyratzis, HERD Collaboration, Latest advancements of the HERD space mission. Nucl. Instrum. Methods Phys. Res. Sect. A. 1048, 167970 (2023). https://doi.org/10.1016/j.nima.2022.167970

- Y. Dong, Overall status of the high energy cosmic radiation detection facility onboard the future China's space station. in *36th International Cosmic Ray Conference (ICRC2019)*. **36**, (2019). https://doi.org/10.22323/1.358.0062

- 21. F.C.T Barbato, The HERD space mission. The Sixteenth Marcel Grossmann Meeting on Recent Developments in Theoretical and Experimental General Relativity, Astrophysics and Relativistic Field Theories: Proceedings of the MG16 Meeting on General Relativity Online, 5–10 July 2021. 3455–3467 (2023). https://doi. org/10.1142/9789811269776\_0284

- Z.H. Xu, Q. Yuan, Z. Tang et al., Potential of constraining propagation parameters of galactic cosmic rays with the high energy cosmic-radiation detection facility onboard China's Space Station. Res. Astron. Astrophys. 23, 085019 (2023). https://doi.org/ 10.1088/1674-4527/acdabd

- B. Huang, H. Liu, X. Huang et al., Side-On transition radiation detector: a detector prototype for TeV energy scale calibration of calorimeters in space. Nucl. Instrum. Methods Phys. Res. Sect. A. 962, 163723 (2020). https://doi.org/10.1016/j.nima.2020.163723

- F. Barbosa, H. Fenker, S. Furletov, et al., A new transition radiation detector based on GEM technology. Nucl. Instrum. Methods Phys. Res. Sect. A. 942, 162356 (2019). https://doi.org/10.1016/j. nima.2019.162356

- A. Andronic, J.P. Wessels, Transition radiation detectors. Nucl. Instrum. Methods Phys. Res. Sect. A. 666, 130–147 (2012). https://doi.org/10.1016/j.nima.2011.09.041

- P. Kähler, F. Roether, CBM collaboration. The transition radiation detector in the CBM experiment at FAIR. Nucl. Instrum. Methods Phys. Res. Sect. A. 958, 162727 (2020). https://doi.org/10.1016/j. nima.2019.162727

- G. Song, Y. Zhao, M. Shao et al., Construction and test of a transition-radiation detector prototype based on thick gas electron multiplier technology. JINS. 18, P01024 (2023). https://doi.org/ 10.1088/1748-0221/18/01/P01024

- J. Adolfsson, A.A. Pabon, M. Bregant et al., SAMPA chip: the new 32 channels ASIC for the ALICE TPC and MCH upgrades. J. Instrum. 12, C04008 (2017). https://doi.org/10.1088/1748-0221/ 12/04/C04008

- A. Velure, Upgrades of the ALICE TPC front-end electronics for long shutdown 1 and 2. IEEE Trans. Nucl. Sci. 62,1040–1044 (2015)

- S.M. Mahmood, Exploring Single Event Effects in the ALICE (A Large Ion Collider Experiment) SAMPA Chip. (2020). https://cds. cern.ch/record/2750379

- Xilinx Corporation, 7 Series FPGAs Data Sheet: Overview. https://docs.xilinx.com/v/u/en-US/ds180\_7Series\_Overview

- A. Velure, A digital signal processor for particle detectors: design, verification and testing. Springer Nature (2021). https://doi.org/ 10.1007/978-3-030-71559-5

- C. Chen, Z. Wang, J. Hu, FPGA remote firmware update method based on SiTCP communication protocol with rollback function. Nucl. Tech. 43, 110401 (2020). https://doi.org/10.11889/j.0253-3219.2020.hjs.43.110401 (in Chinese)

- 34. G. Tambave, A. Velure, Qualification of the ALICE SAMPA ASIC with a high-speed continuous DAQ system. IEEE Trans. Nucl. Sci. 64, 1461–1466 (2017). https://doi.org/10.1109/TNS. 2017.2707339

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.