# Transient radiation effects in CMOS inverters fabricated on SIMOX and BESOI wafers\*

Zhu Shi-Yang (竺土场), Lin Cheng-Lu (林成鲁) (State Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Metallurgy, the Chinese Academy of Sciences, Shanghai 200050)

and Li Jin-Hua (李金华)

(Jiangsu Petrochemical Industry College, Changzhou 213016)

Abstract CMOS inverter circuits are successfully fabricated on thin film SIMOX wafers and thick film BESOI wafers. The output voltage variation is measured with a pulse of  $\gamma$ -ray radiation. Compared with bulk silicon CMOS circuits, SOI circuits have improved the transient radiation hardness significantly.

Keywords Transient radiation effects, SIMOX, BESOI, CMOS

#### 1 Introduction

In recent years, SOI (silicon on insulator) technology has been developed rapidly and is regarded as a primary candidate for the 21 st century ICs (integrated circuits). One of the most important advantages is that SOI circuits are inherently tolerant to transient irradiation and single event upsets.<sup>[1]</sup> Many SOI fabrication techniques have been investigated. Among those, SIMOX (separation by implanted oxygen) and BESOI (bonding and etch-back SOI) are the most potential techniques. [2,3] High quality thin film SIMOX wafers have been fabricated by the multi-implant-and annealing technique. BESOI wafers have high quality Si overlayer and buried oxide, but the etch-back is a difficult process. It is suitable to fabricate thick film SOI wafer. In this paper, CMOS (complementary metal-oxide-semiconductor) inverter circuits have been successfully fabricated on the thin film SIMOX wafers and the thick film BE-SOI wafers. The transient radiation response for the inverters is investigated by measuring output voltage variation with a pulse of  $\gamma$ -ray radiation.

## 2 Experimental

(100) oriented,  $10{\sim}13\Omega{\cdot}\mathrm{cm}$ , P-type, single crystal silicon wafers were implanted by 200 keV O<sup>+</sup> at a dose of  $0.6{\times}10^{18}\mathrm{cm}^{-2}$  and annealed

at 1300°C for 2h in the 0.99 volume fraction Ar+0.01 volume fraction O<sub>2</sub> ambient. After three times implanting and annealing, the Si overlayer thickness and the buried oxide thickness of the final SIMOX wafer are 180 nm and 430 nm, respectively. A standard process (silicon gate, self-alignment, total ion implantation) was used to fabricate the linear gate cc4069 CMOS circuits (six inverters). The silicon island was formed by high temperature oxidation of isolating groove with Si<sub>3</sub>N<sub>4</sub> mask. The gate oxide was grown by dry O2 oxidation and the thickness is 58 nm. The channel width/length ratio is  $128 \,\mu\text{m}/2.5 \,\mu\text{m}$  and  $344 \,\mu\text{m}/2.5 \,\mu\text{m}$  for PMOS and NMOS, respectively. thickness in the active region is approximately 135 nm, so both PMOS and NMOS are fullydepleted.

In dry oxygen ambient at  $1100^{\circ}$ C, 300 nm SiO<sub>2</sub> was grown onto (100) oriented,  $3{\sim}6\Omega{\cdot}\text{cm}$ , N-type, single crystal silicon wafers. After suitable surface treatment they were bonded directly in  $H_2 + O_2$  ambient at  $1200^{\circ}$ C for 2 h. One side of the bonded wafers was thinned down to approximately 6  $\mu$ m by mechanical polishing. The cc4007 CMOS circuits (double complementary pairs and an inverter) were fabricated on the BESOI wafers. P well was pushed into the buried oxide directly. The gate oxide was grown to 98 nm in  $O_2$ ,  $H_2+O_2$ ,  $O_2$  ambients

Manuscript received date: 1996-05-07

<sup>\*</sup>This project is supported by the National Defense Department, which belongs to "85" plan military microelectronics preliminary research project: "SOI/CMOS and Multi-functional Three Dimensional Integrated Circuits" (8.4.3)

at 1000°C sequentially. The channel length is  $7.5 \mu m$ .

The  $\gamma$ -dot experiments were performed at the Chinese Academy of Engineering Physics. The dose rate was  $6.56 \times 10^8$  Gy(Si)/s. The bias condition during irrradiation is  $V_{\rm DD} = 5\,V$ ,  $V_{\rm ss} = 0V$ , the input terminal (1A) of one of the inverters connects to earth, and the corresponding output terminal (1Q) connects with an oscillograph. The residual input terminals connect to earth and the residual output terminals are floating.

### 3 Results and discussion

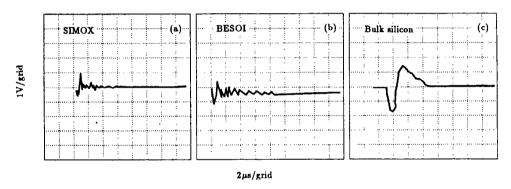

The output voltage variation of the invert-

ers on thin film SIMOX, thick film BESOI and bulk silicon with a pulse of  $\gamma$ -ray radiation is shown in Fig.1(a), (b) and (c), respectively. For SOI devices, there are approximately  $4\mu$ s output disturbance after  $6.56\times10^8$  Gy(Si)/s  $\gamma$ -ray radiation, and the amplitude of SIMOX devices is smaller than that of BESOI devices. For comparison, the output voltage of bulk devices suffers  $2\mu$ s level turnover, followed by  $3.8\mu$ s level rise after  $5.97\times10^8$  Gy(Si)/s  $\gamma$ -ray radiation. The transient radiation hardness of SOI devices is significantly better than that of bulk devices. Furthermore, thin film totally-depleted SOI devices are harder to transient radiation than thick film partly-depleted SOI devices.

Fig.1 The output voltage variation of the inverters on (a) thin film SIMOX, (b) thick film BESOI and (c) bulk silicon with a pulse of  $\gamma$ -ray radiation

It is well known that the prompt transient photocurrent,  $I_{PDS}$ , induced by a pulse of  $\gamma$ -ray radiation, causes the output voltage variation.<sup>[4]</sup> While,

$$I_{\text{PDS}} = q \cdot V_{\text{depl}} \cdot g \cdot \stackrel{\cdot}{D} (t)$$

where  $\dot{D}(t)$  is the dose rate, g is the electronhole generation rate  $(4\times10^{15}\,\mathrm{cm^{-3}\cdot Gy^{-1}(Si)})$ , q is the elementary charge,  $V_{\mathrm{depl}}$  is the depletion volume. SOI devices have smaller  $V_{\mathrm{depl}}$  and eliminate the latch-up effect due to the buried oxide, so the transient radiation hardness is better than that of bulk devices.

#### 4 Conclusion

CMOS circuits have been successfully fab-

ricated on the thin film SIMOX wafers and the thick film BESOI wafers. The transient radiation effects are studied by measuring the output voltage variation with a pulse of  $\gamma$ -ray radiation. Compared with bulk circuits, SOI circuits have excellent hardness to transient radiation.

#### References

- 1 Colinge J P. Silicon-on-insulator technology: materials to VLSI. Kluwer Academic Pub, 1991; Chapter 1

- 2 Hosack H H. NSREC 1991 SAN DIEGO CAL, July 15, 1991

- 3 Stahlbush R E. IEEE Trans Nucl Sci, 1992; 39(6):2086

- 4 Davis G E. IEEE Trans Nucl Sci, 1985; NS-32(6):4432